Feed Crystalfontz [copy] https://www.crystalfontz.com/blog/feed/ has loading error: A feed could not be found at `https://www.crystalfontz.com/blog/feed/`; the status code is `200` and content-type is `text/html; charset=UTF-8`

Feed linux for devices [copy] http://www.linuxfordevices.com/rss-feeds-1.xml has loading error: cURL error 22: The requested URL returned error: 404

Feed marsohod.org [copy] https://marsohod.org/component/ninjarsssyndicator/?feed_id=1&format=raw has loading error: cURL error 22: The requested URL returned error: 500

Feed Music Hackspace [copy] http://musichackspace.org/feed/rss/ has loading error: cURL error 22: The requested URL returned error: 404

Feed SparkFun Electronics [copy] http://www.sparkfun.com/feeds/news has loading error: cURL error 22: The requested URL returned error: 405

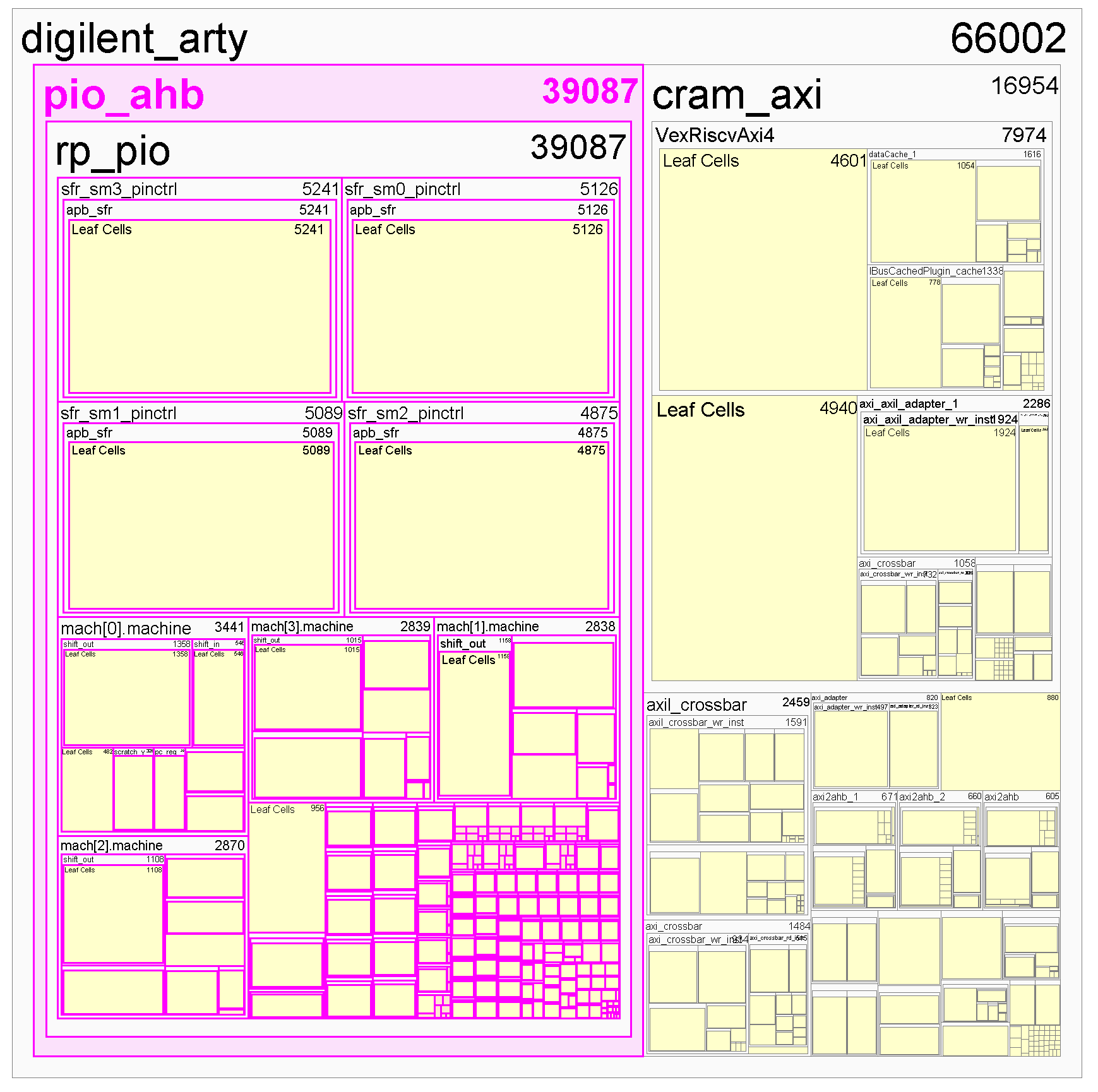

BIO: The Bao I/O Coprocessor

BIO is the I/O co-processor in the Baochip-1x, a mostly open source 22nm SoC I helped design. You can read more about the Baochip-1x’s background here, or pick up an evaluation board at Crowd Supply.

In this post, I’ll talk about the origins of the BIO, starting by working through a detailed study of the Raspberry Pi PIO as a reference, before diving into the architecture of the BIO. I’ll then work through three programming examples of the BIO, two in assembly and one in C. If all you’re interested in is how to use the BIO, you can skip the...

The best laptop Apple ever made

Today I posted a video titled The best laptop Apple ever made, and tl;dw1 it's the 11" MacBook Air.

I acknowledge in the video my pick is slightly subjective, and I also asked a number of other YouTubers which Mac laptop they consider the best (or at least most influential). If you don't want to watch the video, I'll summarize their choices here:

Радио почти из ничего — самодельные радиодетали 1920-х годов. Резисторы

Рассматривая любительские рукодельные электронные лампы, например, [1, 2], интересно и полезно будет вспомнить и об остальных радиоэлементах, изготовлять которые ранним любителям приходилось самостоятельно и собственноручно. Кроме естественных корпусов-ящиков и контурных катушек, дросселей, трансформаторов, коллеги-предки часто были вынуждены делать и почти всё остальное — как установочные элементы — ручки, верньеры, шкалы, клеммы, включатели-переключатели, ламповые панельки, так и радиоэлементы пассивные — резисторы и конденсаторы переменные и постоянные, диоды (детекторы и выпрямители), элементы питания, в том числе и анодные (а это на минуточку — 40…80 вольт!) батареи.

Добавим — всё это предлагалось собирать обычному увлечённому гражданину, юношеству, часто школьнику и из самых чепуховых, буквально подножных...

Как разгоняется электричка? Запускаем блок регулировки ускорения

Приветствую всех!

Раннее летнее утро, пригородная платформа на вокзале одного неназванного города. Пассажиры садятся в стоящую на пути электричку, занимают места и достают обязательную для любой поездки на железной дороге еду. В это время машинист готовится к отправлению, закрывает двери, отпускает тормоза и, наконец, переводит ручку контроллера в ходовое положение.

Казалось бы, всё просто, но многие даже не подозревают, сколько интересного в этот момент происходит. Итак, сегодня разберёмся, как всё это работает, как устроены отвечающие за это блоки и как сжатый воздух помогает электричке плавно трогаться. Заодно запустим один из блоков и увидим его в работе.

Press F1 to continueFree Stuff - January 2026

The January 2026 recipient for the Great Scott Gadgets Free Stuff Program is Hank Fordham, a cybersecurity specialist and public speaker from Alberta, Canada! Hank, better known online as “Hank the Hacker” delivers live hacking demonstrations at conferences, higher education institutions, CTF competitions, and public sector events. We have sent Hank a HackRF One and YARD Stick One to use as core components of these demonstrations at upcoming conferences this year. He tells us that his presentations focus on demystifying wireless attacks by showing audiences how real-world RF threats work in practice. Rather than relying solely on slides, he builds...

Free Stuff - December 2025

The December 2025 recipient for the Great Scott Gadgets Free Stuff Program is Nikos Gerogiannakis, applying on behalf of the Epictetus Wireless Security & Signal Research Initiative at the Hellenic Mediterranean University. Nikos says that their group has established a solid foundation in digital signal analysis and embedded security through hands-on projects such as an FPGA-based logic analyzer and Smart Locker systems. With the HackRF One we have sent their way, the group plans to proactively audit systems like their RFID scanners, probing for real-world vulnerabilities such as signal replay to develop genuinely robust, open-source access controls. They also plan...

Self-Repair Guide for HackRF Pro USB-C Connector

Since HackRF Pro began shipping at the end of 2025, we have become aware of an ongoing issue with USB connectors on some units received by customers. Our engineering team has investigated further and discovered that the connector manufacturer changed tooling between our prototypes and full production, resulting in less reliable ground/shield contact. The next production round has started and we have corrected the issue by using a replacement part, so this issue should only affect units from the r1.2.1-p1 round.

If your HackRF Pro tends to lose USB connectivity easily when the USB cable is touched, first try a different...

Restoring an Xserve G5: When Apple built real servers

Recently I came into posession of a few Apple Xserves. The one in question today is an Xserve G5, RackMac3,1, which was built when Apple at the top—and bottom—of it's PowerPC era.

This isn't the first Xserve—that honor belongs to the G41. And it wasn't the last—there were a few generations of Intel Xeon-powered RackMacs that followed. But in my opinion, it was the most interesting.

Unfortunately, being manufactured in 2004, this Mac's Delta power supply suffers from the Capacitor Plague. The PSU tends to run hot, and some of the capacitors weren't even 105°C-rated, so they tend to wear out, especially...

Microscope Light

[Hardware] Illumination improvements

Фамипия. Оживляем раритетный домофон с тремя ручками

Приветствую всех!

Не так давно я уже рассказывал про раритетный венгерский домофон «Фамипия». И вот очередь дошла до другой панели этой же серии. По виду экземпляр очень похож на домофон «Сезам», отчего зачастую его путают именно с ним. Тем не менее, ничего общего с «тем» сезамом у него нет. «Питерский сезам», «сезам с оптическим ключом», «сезам с кнопкой освещения» — это всё он.

Самое время узнать, как он устроен, и попробовать его запустить. Именно этим мы сейчас и займёмся...

Нажать и не отпускать до конца разговора